High-Power, Quad, Monolithic, PSE Controllers

for Power over Ethernet

______________________________________________________________________________________ 35

Setting DET_EN_/CLASS_EN_ to 1 (Table 18) enables

load detection/classification, respectively. Detection

always has priority over classification. To perform clas-

sification without detection, set the DET_EN_ bit low

and CLASS_EN_ bit high.

In manual mode, R14h works like a pushbutton. Set the

bits high to begin the corresponding routine. The bit

clears after the routine finishes.

When entering auto mode, R14h defaults to FFh. When

entering semi or manual modes, R14h defaults to 00h.

A reset or power-up sets R14h = AAAAAAAAb where A

represents the latched-in state of the AUTO input prior

to the reset.

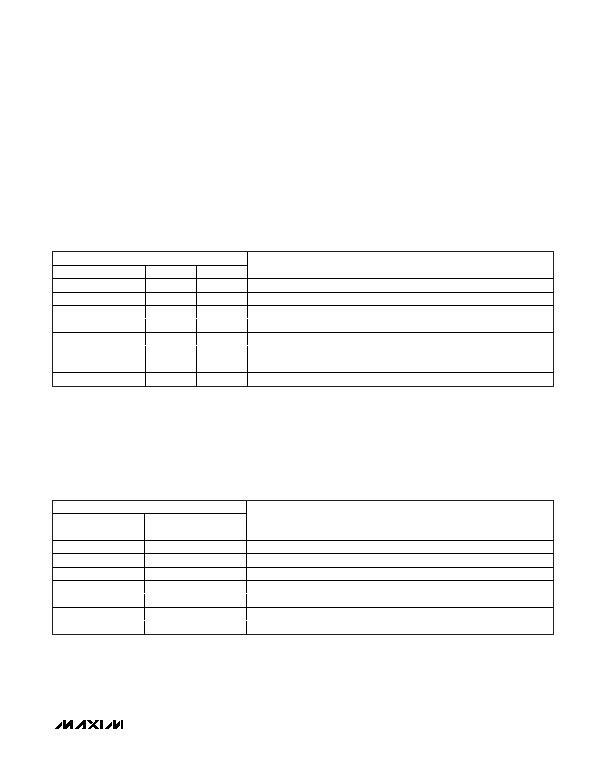

Table 18. Detection and Classification Enable Register

ADDRESS = 14h

SYMBOL

BIT

R/W

DESCRIPTION

CLASS_EN4

7

R/W

Enable classification on port 4

CLASS_EN3

6

R/W

Enable classification on port 3

CLASS_EN2

5

R/W

Enable classification on port 2

CLASS_EN1

4

R/W

Enable classification on port 1

DET_EN4

3

R/W

Enable detection on port 4

DET_EN3

2

R/W

Enable detection on port 3

DET_EN2

1

R/W

Enable detection on port 2

DET_EN1

0

R/W

Enable detection on port 1

Table 19. Backoff and High-Power Enable Register

ADDRESS = 15h

SYMBOL

BIT

R/W

DESCRIPTION

EN_HP_ALL

7

R/W

High-power detection enabled

EN_HP_CL6

6

R/W

Class 6 PD high-power enabled

EN_HP_CL5

5

R/W

Class 5 PD high-power enabled

EN_HP_CL4

4

R/W

Class 4 PD high-power enabled

BCKOFF4

3

R/W

Enable cadence timing on port 4

BCKOFF3

2

R/W

Enable cadence timing on port 3

BCKOFF2

1

R/W

Enable cadence timing on port 2

BCKOFF1

0

R/W

Enable cadence timing on port 1

EN_HP_CL_, EN_HP_ALL together with CL_DISC

(R17h[2]) and ENx_CL6 (R1Ch[7:4]) are used to program

the high-power mode. See Table 3 for details.

Setting BCKOFF_ to 1 (Table 19) enables cadence tim-

ing on each port where the port backs off and waits

2.2s after each failed load discovery detection. The

IEEE 802.3af standard requires a PSE that delivers

power through the spare pairs (midspan PSE) to have

cadence timing.

A reset or power-up sets R15h = 0000XXXXb where X

is the logic AND of the MIDSPAN and AUTO inputs.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MAX5969DETE+T

IC CTRLR INTERFCE W/MOSFT 16TQFN

MAX5971AETI+

IC CTRLR PD IEEE 802.3AF 28WQFN

MAX5972AETE+T

IC CONTROLLER INTERFACE 16TQFN

MAX5978ETJ+

IC CTLR HOT-SWAP 32TQFN

MAX5981BETE+

IC CTRLR PD IEEE 802.3AF 16TQFN

MAX5986AETE+

IC POE SWITCH PSE 16TQFN

MAX6509CAZK/V+T

IC TEMP SWITCH RES-PROG 5TSOT

MAX6513TT075+T

IC TEMP SWITCH REMOTE 6-TDFN

相关代理商/技术参数

MAX5965AEAX+T

功能描述:热插拔功率分布 Quad PSE Controller for POE RoHS:否 制造商:Texas Instruments 产品:Controllers & Switches 电流限制: 电源电压-最大:7 V 电源电压-最小:- 0.3 V 工作温度范围: 功率耗散: 安装风格:SMD/SMT 封装 / 箱体:MSOP-8 封装:Tube

MAX5965AUAX+

功能描述:热插拔功率分布 Quad PSE Controller for POE RoHS:否 制造商:Texas Instruments 产品:Controllers & Switches 电流限制: 电源电压-最大:7 V 电源电压-最小:- 0.3 V 工作温度范围: 功率耗散: 安装风格:SMD/SMT 封装 / 箱体:MSOP-8 封装:Tube

MAX5965AUAX+T

功能描述:热插拔功率分布 Quad PSE Controller for POE RoHS:否 制造商:Texas Instruments 产品:Controllers & Switches 电流限制: 电源电压-最大:7 V 电源电压-最小:- 0.3 V 工作温度范围: 功率耗散: 安装风格:SMD/SMT 封装 / 箱体:MSOP-8 封装:Tube

MAX5965BCAX+

制造商:Maxim Integrated Products 功能描述:- Rail/Tube

MAX5965BCAX+T

制造商:Maxim Integrated Products 功能描述:HIGH-POWER, QUAD, MONOLITHIC, PSE CONTROLLERS FOR POWER OVER - Tape and Reel

MAX5965BEAX+

功能描述:热插拔功率分布 Quad PSE Controller for POE RoHS:否 制造商:Texas Instruments 产品:Controllers & Switches 电流限制: 电源电压-最大:7 V 电源电压-最小:- 0.3 V 工作温度范围: 功率耗散: 安装风格:SMD/SMT 封装 / 箱体:MSOP-8 封装:Tube

MAX5965BEAX+T

功能描述:热插拔功率分布 Quad PSE Controller for POE RoHS:否 制造商:Texas Instruments 产品:Controllers & Switches 电流限制: 电源电压-最大:7 V 电源电压-最小:- 0.3 V 工作温度范围: 功率耗散: 安装风格:SMD/SMT 封装 / 箱体:MSOP-8 封装:Tube

MAX5965BUAX+

功能描述:热插拔功率分布 Quad PSE Controller for POE RoHS:否 制造商:Texas Instruments 产品:Controllers & Switches 电流限制: 电源电压-最大:7 V 电源电压-最小:- 0.3 V 工作温度范围: 功率耗散: 安装风格:SMD/SMT 封装 / 箱体:MSOP-8 封装:Tube